## Robustness between Weak Memory Models

Soham Chakraborty

EEMCS, TU Delft

FMCAD 2021

## What is Weak Memory Model?

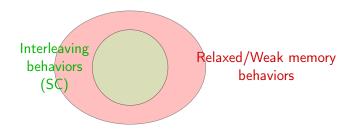

Traditionally: concurrency = thread interleaving

### What is Weak Memory Model?

Traditionally: concurrency = thread interleaving

Reality: more behaviors than thread interleaving

### Example: SB

$$X = Y = 0;$$

(1)  $X = 1;$  | (3)  $Y = 1;$

(2)  $a = Y;$  | (4)  $b = X;$

**Behaviors:** SC Interleavings

$$a = 1, b = 1$$

$\checkmark$  1-3-2-4, 3-1-4-2, ...  $a = 0, b = 1$   $\checkmark$  1-2-3-4  $a = 1, b = 0$   $\checkmark$  3-4-1-2  $a = 0, b = 0$   $\checkmark$

## Example: SB

$$X = Y = 0;$$

(1)  $X = 1;$  | (3)  $Y = 1;$

(2)  $a = Y;$  | (4)  $b = X;$

Behaviors: SC x86

$$a = 1, b = 1$$

$\checkmark$   $\checkmark$

$a = 0, b = 1$   $\checkmark$   $\checkmark$

$a = 1, b = 0$   $\checkmark$   $\checkmark$

$a = 0, b = 0$   $\checkmark$   $\checkmark$

### Example: SB+mfences

$$X = Y = 0;$$

$X = 1;$

MFENCE;

$a = Y;$

$Y = 1;$

MFENCE;

$b = X;$

Behaviors: SC x86

$$a = 1, b = 1$$

$\checkmark$   $\checkmark$

$a = 0, b = 1$   $\checkmark$   $\checkmark$

$a = 1, b = 0$   $\checkmark$   $\checkmark$

$a = 0, b = 0$   $\checkmark$   $\checkmark$

### Examples: SB+mfences and SB

$$X = Y = 0;$$

$X = 1;$

MFENCE;

$a = Y;$

$Y = 1;$

MFENCE;

$b = X;$

$$X = Y = 0;$$

$X = 1;$  |  $Y = 1;$

$a = Y;$  |  $b = X;$

| Behaviors:   | SC | x86 |

|--------------|----|-----|

| a = 1, b = 1 | 1  | 1   |

| a = 0, b = 1 | ✓  | ✓   |

| a = 1, b = 0 | 1  | ✓   |

| a = 0, b = 0 | X  | X   |

Behaviors: SC x86

$$a = 1, b = 1$$

$\checkmark$   $\checkmark$

$a = 0, b = 1$   $\checkmark$   $\checkmark$

$a = 1, b = 0$   $\checkmark$   $\checkmark$

$a = 0, b = 0$   $\checkmark$   $\checkmark$

Some (not all) programs exhibit additional behaviors on weaker models

## Checking (SC) Robustness

Check: For a given program P, and a memory model K: Does running P on K have extra behavior w.r.t. SC?

## Checking (SC) Robustness

Check: For a given program P, and a memory model K = x86: Does running P on K have extra behavior w.r.t. SC?

### Example:

$$X = Y = 0;$$

$X = 1;$  |  $Y = 1;$

$a = Y;$  |  $b = X;$

Violates SC-robustness

## Checking and Enforcing (SC) Robustness

Check: For a given program P, and a memory model K = x86: Does running P on K have extra behavior w.r.t. SC?

Enforce (if program P violates SC-robustness on K): Transform P to P' such that P' is SC-robust.

### **Example:**

$$X = Y = 0;$$

$X = Y = 0;$   $X = 1;$   $Y = 1;$   $X = Y = 0;$   $X = 1;$   $Y = 1;$

Violates SC-robustness

Enforce SC-robustness

## Checking and Enforcing (SC) Robustness

Check: For a given program P, and a memory model K = x86: Does running P on K have extra behavior w.r.t. SC?

Enforce (if program P violates SC-robustness on K): Transform P to P' such that P' is SC-robust.

### Example:

$$X = Y = 0;$$

$X = Y = 0;$   $X = 1;$   $Y = 1;$   $X = Y = 0;$   $X = 1;$   $Y = 1;$

Violates SC-robustness

Enforce SC-robustness

Enable translation of a program from model K to SC

### This Paper

Checking and enforcing robustness of x86 and ARM (Version 8 and 7) concurrent programs

#### **SC-Robustness**

For a given program P, and a memory model K:

Does running P on K have extra behavior w.r.t. SC?

#### M-K Robustness

For a given program P, and two memory models M and K: Does running P on K have extra behavior w.r.t. M?

For a given program P, and two memory models M and K: Does running P on K have extra behavior w.r.t. M?

**Existing approaches:** *M*=sequential consistency (SC)

| $\downarrow$ M-K $\rightarrow$ | x86      | ARMv8 | ARMv7 |

|--------------------------------|----------|-------|-------|

| SC                             | <b>√</b> | ?     | ?     |

| x86                            | -        | ?     | ?     |

| ARMv8                          | -        | -     | ?     |

For a given program P, and two memory models M and K: Does running P on K have extra behavior w.r.t. M?

**Existing approaches:** *M*=sequential consistency (SC)

| $\downarrow$ M-K $\rightarrow$ | x86      | ARMv8 | ARMv7 |

|--------------------------------|----------|-------|-------|

| SC                             | <b>√</b> | ✓     | ✓     |

| x86                            | -        | ?     | ?     |

| ARMv8                          | -        | -     | ?     |

For a given program P, and two memory models M and K: Does running P on K have extra behavior w.r.t. M?

**Existing approaches:** *M*=sequential consistency (SC)

| $\downarrow$ M-K $\rightarrow$ | x86      | ARMv8 | ARMv7 |

|--------------------------------|----------|-------|-------|

| SC                             | <b>✓</b> | ✓     | ✓     |

| x86                            | -        | ✓     | ✓     |

| ARMv8                          | -        | -     | ✓     |

### x86 to ARM Translation

$$X = Y = 0;$$

Behaviors:

SC x86 ARM

$X = 1;$

$Y = 1;$

$X = 1;$

The program is x86-ARM robust

SC-robustness for ARM is too strong for x86 to ARM translation

• The inserted DMBFULL fences are redundant

### x86 to ARM Translation

$$X=Y=0;$$

Behaviors: SC x86 ARM  $X=1;$   $Y=1;$   $X=1,b=1$   $X=1,b=1$

The program is x86-ARM robust

SC-robustness for ARM is too strong for x86 to ARM translation

• The inserted DMBFULL fences are redundant

For a given program P, and two memory models M and K: Does running P on K have extra behavior w.r.t. M?

**Existing approaches:** *M*=sequential consistency (SC)

| $\downarrow$ M-K $\rightarrow$ | x86 | ARMv8 | ARMv7 |

|--------------------------------|-----|-------|-------|

| SC                             | 1   | ✓     | ✓     |

| x86                            | -   | ✓     | ✓     |

| ARMv8                          | -   | -     | ✓     |

### Proposed Approach:

- Identify M-K robustness conditions

- Statically analyze if a program is M-K robust

- If not: Insert appropriate fences to enforce robustness

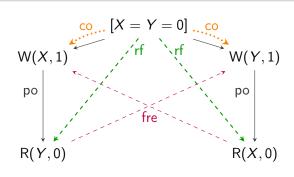

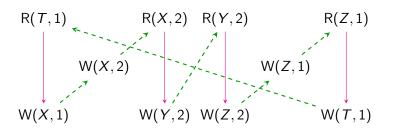

## SB Execution Graph

$$X = Y = 0;$$

$X = 1;$   $Y = 1;$

$a = Y;$   $b = X;$

Outcome:

$a = b = 0$

## SB Execution Graph

$$X = Y = 0;$$

$X = 1;$   $Y = 1;$

$a = Y;$   $b = X;$

Outcome:

$a = b = 0$

po: program order

rf: reads-from

co: coherence-order

fr: from-read

rfe: external-reads-from

coe: external-coherence-order

fre: external-from-read

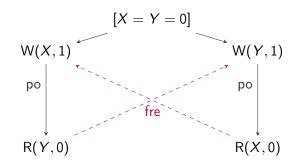

## SB Execution Graph

$$X = Y = 0;$$

$X = 1;$  |  $Y = 1;$

$a = Y;$  |  $b = X;$

$a = b = 0$

SC-robustness violation by po  $\cup$  fre cycle

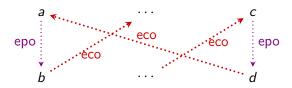

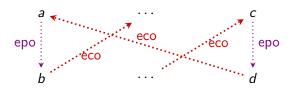

### Some Definitions

- $eco = (rfe \cup coe \cup fre)^+$  and

- $epo = po \cap (codom(eco) \times dom(eco))$

## Proposed Technique

An axiom violation implies a cycle on the execution graph

An axiom violating cycle is of the form:

where at least one epo is unordered

### *M-K* Robustness violating cycle:

allowed in model K but disallowed in model M

## Enforcing Robustness: Breaking the Cycle

Enforce ordering on epo edges

### Possible ways to order memory access pairs in architectures:

- Memory accesses are ordered

- Preserved-program-orders based on dependencies

- Same location memory accesses

- Intermediate fences

## Orderings in Model K

| $\begin{array}{c} Model\ \mathcal{K}\ \Rightarrow \\ Ordering \\ constraints \end{array}$ | ×86 | ARMv8 | ARMv7 |

|-------------------------------------------------------------------------------------------|-----|-------|-------|

| Regular Memory accesses                                                                   | /   |       |       |

| synchronizing memory accesses                                                             | _   |       |       |

| Dependency based ordering                                                                 | _   |       |       |

| Same location access pairs                                                                | /   |       |       |

| Intermediate fences                                                                       | /   |       |       |

## Orderings in Model K

| $\begin{array}{c} Model\ \mathcal{K}\ \Rightarrow \\ \downarrow \ Ordering \\ constraints \end{array}$ | ×86 | ARMv8    | ARMv7 |

|--------------------------------------------------------------------------------------------------------|-----|----------|-------|

| Regular Memory accesses                                                                                | 1   | ×        |       |

| synchronizing memory accesses                                                                          | -   | <b>/</b> |       |

| Dependency based ordering                                                                              | -   | <b>/</b> |       |

| Same location access pairs                                                                             | /   | <b>✓</b> |       |

| Intermediate fences                                                                                    | /   | <b>/</b> |       |

## Orderings in Model K

| $\begin{array}{c} Model\ \mathcal{K}\ \Rightarrow \\ \downarrow  Ordering \\ constraints \end{array}$ | ×86 | ARMv8    | ARMv7    |

|-------------------------------------------------------------------------------------------------------|-----|----------|----------|

| Regular Memory accesses                                                                               | 1   | ×        | ×        |

| synchronizing memory accesses                                                                         | _   | <b>/</b> | _        |

| Dependency based ordering                                                                             | _   | <b>✓</b> | <b>✓</b> |

| Same location access pairs                                                                            | /   | <b>/</b> | Х        |

| Intermediate fences                                                                                   | /   | <b>✓</b> | <b>✓</b> |

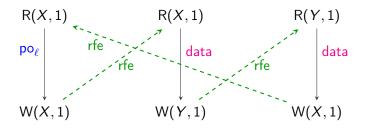

### ARMv7 Concurrency

Same location read-write accesses are not always ordered

$$X = Y = 0;$$

$a = X;$

$X = 1;$   $Y = X;$   $X = Y;$

ARMv7 allows the following execution

Yet poℓ is included in SC-ARMv7 condition

### ARMv7 Concurrency

Dependencies are not strong enough relation (unlike ARMv8)

$$X = T$$

;  $|| X = 2$ ;  $|| Y = X$ ;  $|| Z = Y$ ;  $|| Z = 1$ ;  $|| T = Z$ ;

ARMv7 allows the following execution

The execution is NOT SC-ARMv7 even if all epo edges are ppo

### Robustness Conditions

Conditions for M-K Robustness: all epo edges are ordered

| $\begin{array}{c} Model\ K \ \Rightarrow \\ \downarrow \ Ordering \\ constraints \end{array}$ | ×86 | ARMv8    | ARMv7      |

|-----------------------------------------------------------------------------------------------|-----|----------|------------|

| Regular Memory accesses                                                                       | >   | ×        | ×          |

| synchronizing memory accesses                                                                 | -   | /        | _          |

| Dependency based ordering                                                                     | -   | <b>✓</b> | ✓ <b>X</b> |

| Same location access pairs                                                                    | 1   | <b>✓</b> | × ✓        |

| Intermediate fences                                                                           | 1   | /        | <b>/</b>   |

Static checking of the semantic robustness property **Steps**:

- Identify program components which may run concurrently

- Thread functions which may create multiple threads

Static checking of the semantic robustness property

### Steps:

- Identify program components which may run concurrently

- Construct memory-access pair graph (MPG)

Static checking of the semantic robustness property

### Steps:

- Identify program components which may run concurrently

- Construct memory-access pair graph (MPG)

- Identify the access pairs on the cycle

Static checking of the semantic robustness property

### Steps:

- Identify program components which may run concurrently

- Construct memory-access pair graph (MPG)

- Identify the access pairs on the cycle

- Check if any access pair on the cycle may create an unordered epo

## Implementation and Experiments

Fency: a tool for static robustness analysis and enforcement

- x86, ARMv8, ARMv7 programs

- Based on LLVM code generation phase

- Parameterized programs

#### **Experiments**

- Several concurrent data structures and algorithms

- Compared to Trencher: an existing SC-x86 robustness analyzer

## Fency vs Naive for SC-x86 robustness

### Fency ensures SC-x86 robustness with less fences

| Prog.       | Naive | Fency |

|-------------|-------|-------|

| Barrier     | 6     | 2     |

| Dekker-TSO  | 20    | 4     |

| Peterson-SC | 14    | 2     |

| Lamport-SC  | 17    | 4     |

| Spinlock    | 14    | 0     |

| Ticketlock  | 12    | 0     |

| Seqlock     | 7     | 0     |

| RCU-offline | 33    | 7     |

| Cilk-TSO    | 22    | 2     |

| Cilk-SC     | 22    | 0     |

|             |       |       |

## Fency vs Trencher for SC-x86 robustness

### Checking results and # inserted fences

| Prog.       | Fency      | Trencher   |

|-------------|------------|------------|

| Barrier     | <b>X</b> 2 | <b>X</b> 2 |

| Dekker-TSO  | <b>√</b> 0 | <b>√</b> 0 |

| Peterson-SC | <b>X</b> 2 | <b>X</b> 2 |

| Lamport-SC  | <b>X</b> 4 | <b>X</b> 4 |

| Spinlock    | <b>√</b> 0 | <b>√</b> 0 |

| Ticketlock  | <b>√</b> 0 | <b>√</b> 0 |

| Seqlock     | <b>√</b> 0 | <b>√</b> 0 |

| RCU-offline | <b>X</b> 3 | Х -        |

| Cilk-TSO    | <b>√</b> 0 | <b>√</b> 0 |

| Cilk-SC     | <b>✓</b> 0 | <b>x</b> 2 |

## Analysis time: Fency vs Trencher

| Drog        | Fency       |                           | Tre         | encher                    |

|-------------|-------------|---------------------------|-------------|---------------------------|

| Prog.       | result      | $\langle seconds \rangle$ | result      | $\langle seconds \rangle$ |

| Barrier     | <b>X</b>  2 | ⟨0.005                    | <b>X</b>  2 | ⟨0.004                    |

| Dekker-TSO  | <b>√</b>  0 | ⟨0.002                    | <b>√</b>  0 | ⟨0.007                    |

| Peterson-SC | <b>X</b>  2 | ⟨0.004                    | <b>X</b>  2 | ⟨0.013                    |

| Lamport-SC  | <b>X</b>  4 | ⟨0.019                    | <b>X</b>  4 | ⟨0.107                    |

| Spinlock    | <b>√</b>  0 | ⟨0.004                    | <b>√</b>  0 | ⟨0.007                    |

| Ticketlock  | <b>√</b>  0 | ⟨0.004                    | <b>√</b>  0 | ⟨0.006                    |

| Seqlock     | <b>√</b>  0 | ⟨0.004                    | <b>√</b>  0 | ⟨0.582                    |

| RCU-offline | <b>X</b>  3 | ⟨0.038                    | X  -        | ⟨0.246                    |

| Cilk-TSO    | <b>√</b>  0 | ⟨0.011                    | <b>√</b>  0 | ⟨2.039                    |

| Cilk-SC     | <b>√</b>  0 | ⟨0.010                    | <b>x</b>  2 | ⟨6.322                    |

## Other Observations from Empirical Evaluation

Most of the ARM (8 and 7) programs violate robustness criteria

• Independent memory access pairs are unordered

### Other Observations from Empirical Evaluation

Most of the ARM (8 and 7) programs violate robustness criteria

• Independent memory access pairs are unordered

Enforcing non-SC robustness often requires less fences than enforcing SC-robustness.

• Robustness analyses between weak memory models are useful!

### Conclusion and Future Work

Robustness analysis and enforcement

• x86, ARMv8, ARMv7 programs

Fency: static robustness checking and enforcement

Available at:

```

https://www.st.ewi.tudelft.nl/sschakraborty/Fency-FMCAD21.zip

```

### Going forward:

• New architectures, features, precise and scalable analysis tools

### Conclusion and Future Work

Robustness analysis and enforcement

• x86, ARMv8, ARMv7 programs

Fency: static robustness checking and enforcement

Available at:

```

https://www.st.ewi.tudelft.nl/sschakraborty/Fency-FMCAD21.zip

```

### Going forward:

• New architectures, features, precise and scalable analysis tools

# Thank you!